What is not OK, is continuing using blocking assignments in "q = q << 1" and in "q = tmp". Secondly, in you else statement, you are using a blocking assignment in "tmp = q" which is ok, because it stores q value in a variable internal to the process. And I am not sure if I follow why you are using it, given you have already a reset state for it. My guess is that the state never goes off from s0.Īny tips on how I should implement the codes?įirst of all, initial commands are not used in synthesizable Verilog code. When I run a test cases on it, it somehow only prints s0 and seems to be constant throughout the execution. When control variable is 0, I want to execute s0,s1,s2,s3,s4,s5, and so on as you can see(BCD), and when control variable is 1, I want to execute s0,s1,s3,s2,s6,s7,s5,s4 respectively (gray code) 2nd state: 001, 3rd state: 010 and so on Reg state // there will be 8 states: 1st state :000 Here is my implementation: module grayBCDcounter(

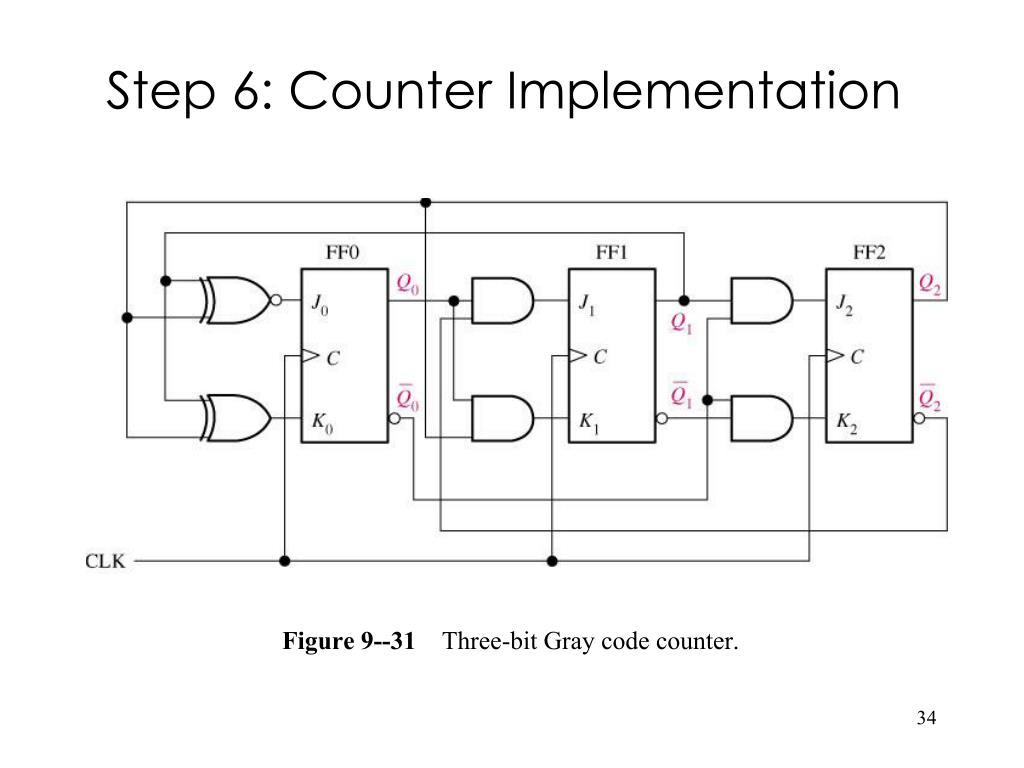

If the input control = 0, the circuit will count in BCD and if the input control = 1, the circuit will count in gray code sequence. I am trying to implement a 8-bit counter that does both BCD(Binary Code decimal) and gray code sequence.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed